4 bit multiplier circuit diagram Block diagram of array multiplier for 4 bit numbers Circuit diagram for booth's algorithm

Booth Multiplier

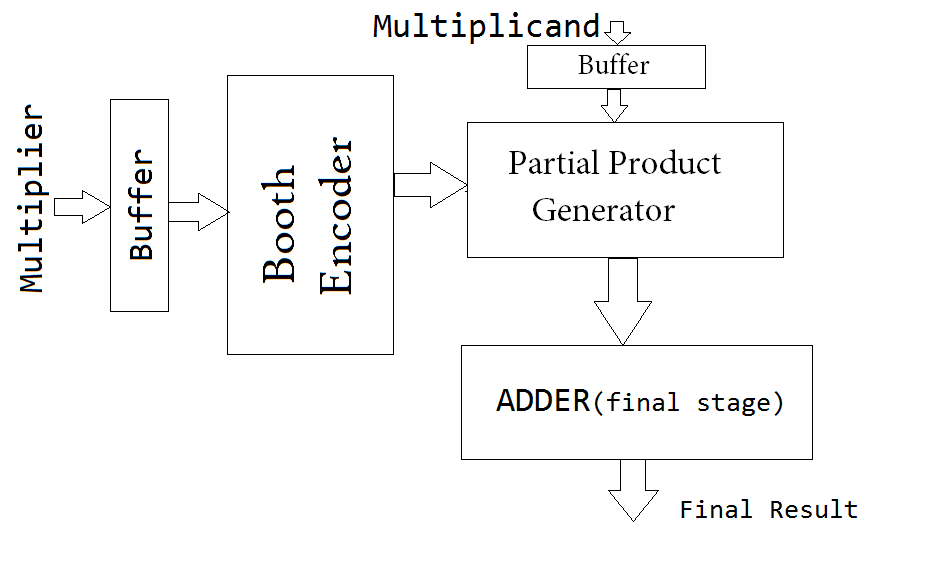

Parallel architecture of proposed radix-4 8-bit booth multiplier

Radix-4 booth multiplier algorithm using combined p and b register for

Multiplier numbersMultiplier radix 4 bit booth multiplier verilog code4 × 4 reversible booth's multiplier [3]..

Low‐power‐delay‐product radix‐4 8*8 booth multiplier in cmos4 bit booth multiplier circuit diagram Virtual labsMultiplier bit structure.

Virtual labs

Figure 1 from design of configurable booth multiplier using dynamicBooth's array multiplier 4-bit multiplier4 bit booth multiplier circuit diagram.

Structure of a 4-bit multiplier.4 bit booth multiplier circuit diagram Design a 4 bit multiplierBooth multiplier.

Multiplier vlsi implementation architectures

4 bit multiplier circuit diagramBooth's algorithm (hardware implementation and flowchart) Four bit multiplier design.4 bit multiplier circuit.

3 bit full adderElectrical – 4 by 4 bit multiplier. logisim help – valuable tech notes Traditional 4 bit array multiplier.Full adder circuit diagram using logic gates.

Booth algorithm hardware flowchart implementation booths algo coa

Multiplier bit4 bit booth multiplier circuit diagram Multiplier array[diagram] 8 bit multiplier circuit diagram.

4 bit booth multiplier circuit diagram4 bit booth multiplier circuit diagram Electrical – 4 by 4 bit multiplier. logisim help – valuable tech notesThe traditional 8×8 radix-4 booth multiplier with the modified sign.